#5 [ModelSim] 프로젝트 생성, 에디팅, 컴파일, 시뮬레이트

15단계로 이루어진 ModelSim 개발도구기반 프로젝트 생성, 에디팅, 컴파일, 시뮬레이트

본 게시물은 프로젝트 생성, 에디팅, 컴파일, 시뮬레이트

과정을 실제로 진행하면서 작성하였습니다.

(작성 기준 : 2019.09.23)

(게시 확인 : 2023.01.04)

< 개발 환경 >

CPU : E3-1231 v3 3.40GHz (8 CPUs)

RAM : 24GB

OS : Windows 10 Pro 64bit

Tool : ModelSim PE Student Edition 10.4a

1. 프로젝트 생성 메뉴 선택

- 개발도구 맨 상단 메뉴 중 File 선택하여 New -> Project 클릭

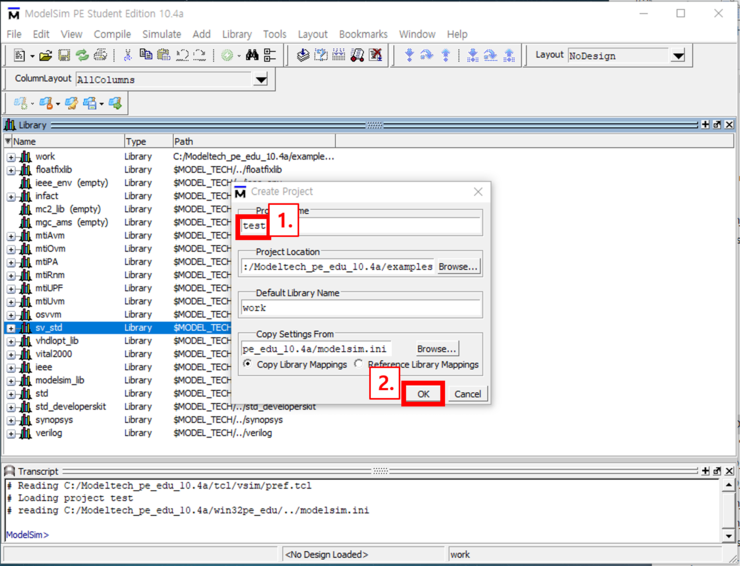

2. 프로젝트 생성

- Project 이름 입력 후 확인 버튼 클릭

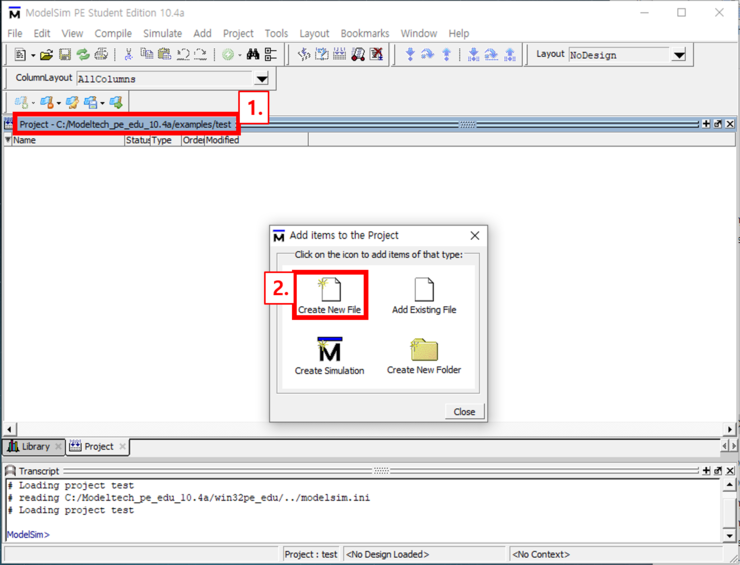

3. 프로젝트 생성 확인 및 Editing 파일 생성 메뉴

- 입력한 이름으로 프로젝트를 확인한 다음, Editing 파일 생성 메뉴 선택

4. Verilog 파일 설정 및 생성

- Editing 파일 생성 메뉴를 선택 시 파일을 설정할 수 있는 창이 뜸

- Add file as type 은 Verilog 로 선택하고 파일 이름을 입력하여 확인 버튼 클릭

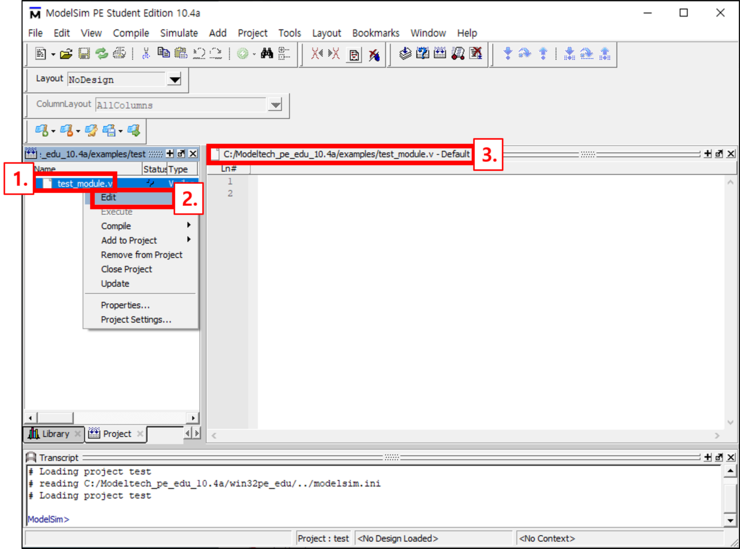

5. 생성된 Verilog 파일 확인 밎 에디팅

- 왼쪽에 프로젝트 탐색기 영역에 생성된 Verilog 파일 확인 (Verilog 확장자는 .v 이다)

- 에디팅은 해당 파일을 더블 클릭 또는 오른쪽 마우스를 클릭하여 Edit 선택하면 영역이 나옴

6. Verilog 파일 추가 생성

- 파일을 추가적으로 생성할 경우 프로젝트 탐색기 영역에 오른쪽 마우스를 클릭하여 Add to Project 를 선택하여 New File 를 선택

- "4. Verilog 파일 설정 및 생성" 과 같은 화면이 나타나므로 참고하길 바람

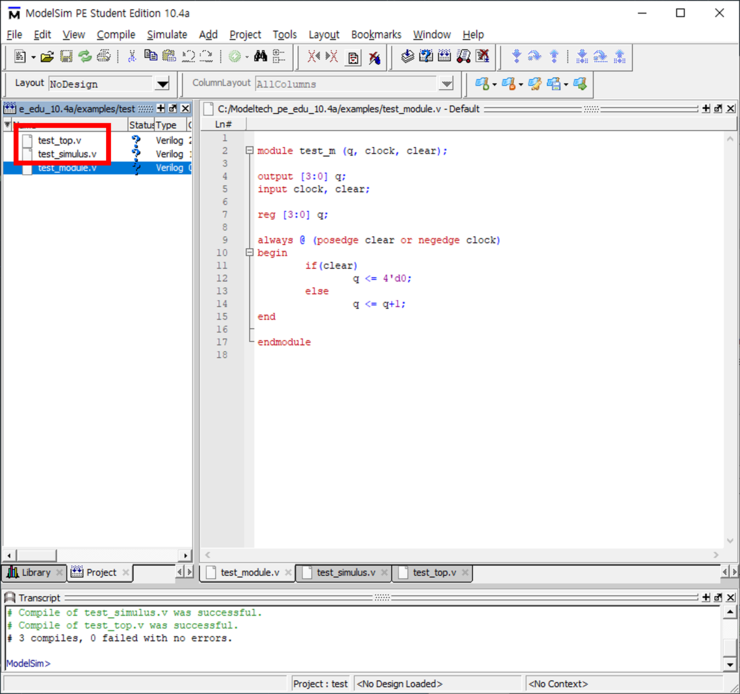

7. 추가적으로 생성된 Verilog 파일 확인

8. 각 Verilog 파일마다 에디팅

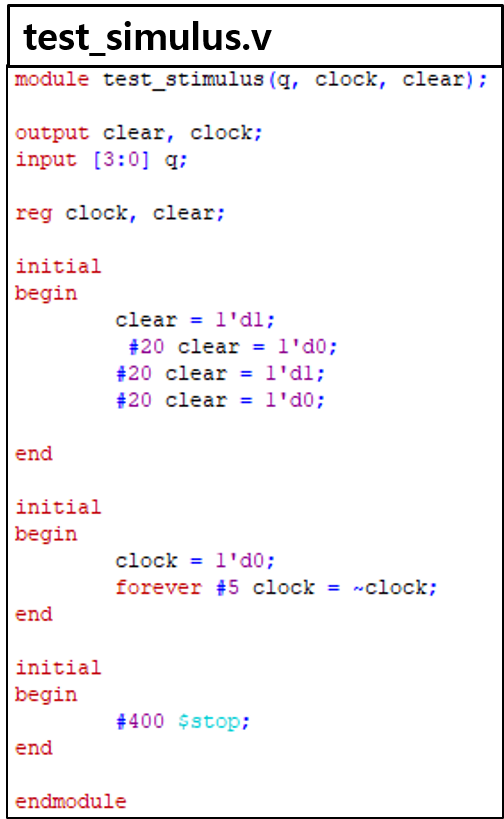

- Verilog 소스는 3가지로 작성하였으며, 해당 파일에 맞게 작성 바람

- 아래 소스 중 test_stimulus 인데 test_simulus 오타가 있지만 시뮬레이트에 문제없음

9. 에디팅 주의사항

- 파일 에디팅 시 저장을 자주해야 합니다.

- 그 이유는, 개발도구가 최적화 및 인터페이스가 좋지 않습니다.

- 버벅임은 기본이고 Visual Studio 개발도구는 에디팅한 파일을 따로 저장하지 않고 바로 디버깅 또는 릴리즈로 동작 시 파일이 자동적으로 저장되지만 ModelSim은 저장된 파일만 컴파일을 하기 때문에 저장을 자주해주어야 합니다.

- 그리고 프로그램이 꺼지는 현상도 나타납니다.

10. 컴파일

- 프로젝트 탐색기에 Status에 "?" 표시는 현재 컴파일이 되지 않은 상태

- 프로젝트 탐색기 영역에 오른쪽 마우스를 클릭하여 Compile -> Compile All 선택하면 생성된 Verilog 파일들을 컴파일함

- 특정 파일만 컴파일을 하고 싶다면 Compile Selected 선택하길 바람

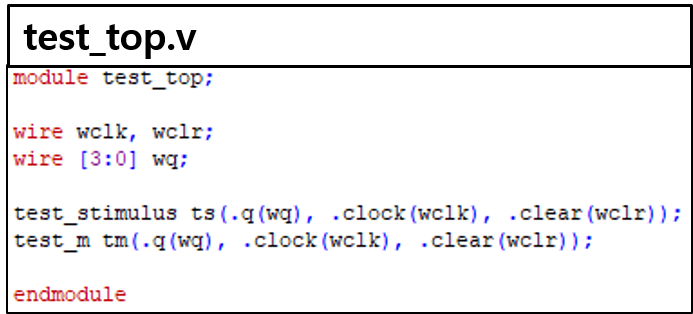

11. 컴파일 시 에러 발생하는 경우

- 에러가 발생된 경우 프로젝트 탐색기에서 컴파일이 완료된 파일은 체크 모양으로 나타나고, 에러 또는 실패한 경우 X 모양으로 나타남

- 해당 에러가 발생되는 원인을 알고 싶다면 맨 하단에 에러 개수와 발생된 파일에 대해 출력함

- 출력된 문자열을 더블 클릭하면 에러창이 나타나고, 에러 발생된 파일명과 그 파일에서 몇번째 라인에서 에러가 나타나는지 알려줌

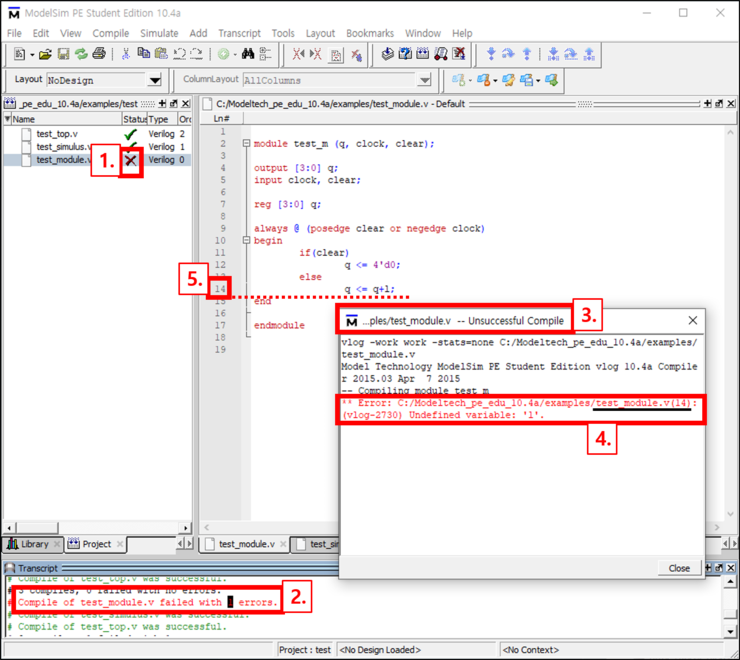

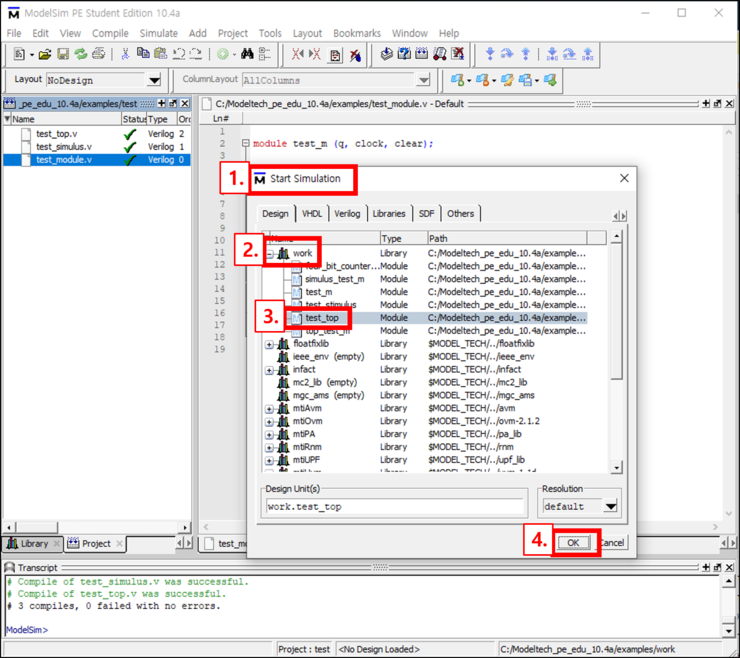

12. 컴파일이 완료한 경우

- 컴파일이 모두 완료된 상태를 확인하고, Wave 시뮬레이트를 실행함

- 맨 상단 메뉴 중 Simulate -> Start Simulation 메뉴 선택

- 또는 아래 사진과 같이 3번의 아이콘을 찾아 클릭하면 시뮬레이트를 실행함

13. 시뮬레이트 실행

- 시뮬레이트 창이 나타나면서, 실행할 파일을 선택함

- Work -> test_top 을 선택하여 확인 버튼 클릭함

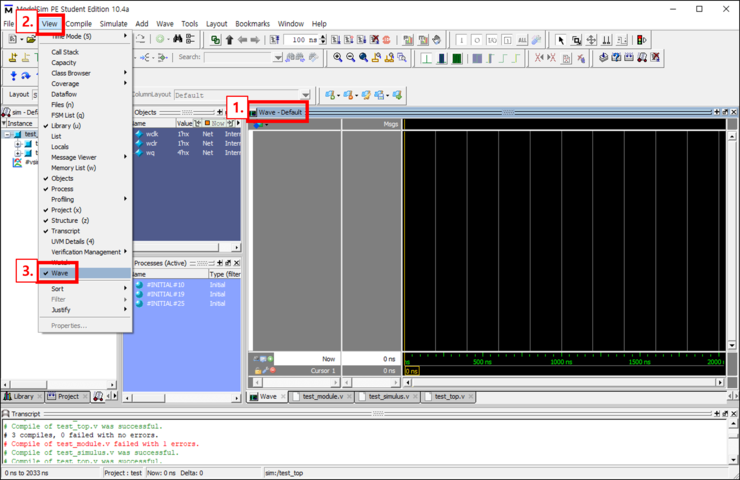

14. Wave 창이 보이지 않는 경우

- 맨 상단 메뉴 중 View 선택하여 Wave를 선택

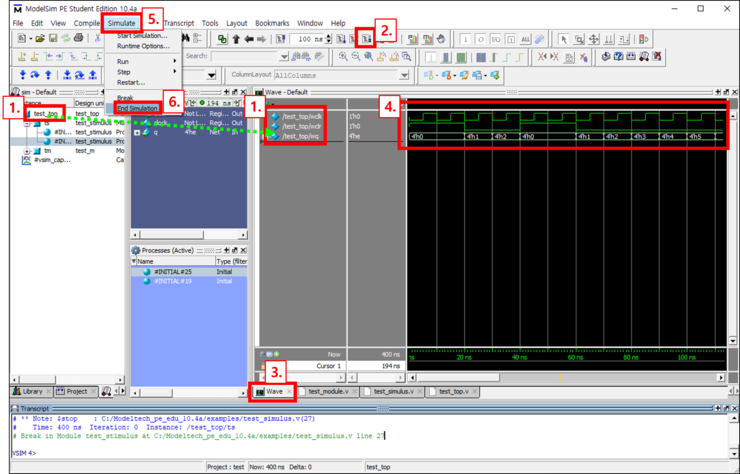

15. 시뮬레이트 동작

- 아래 그림과 같이 맨 왼쪽에 위치한 sim 영역에서 1번인 test_top 을 선택하여, 마우스 드래그로 Wave 창에 끌어옮기면 Object 들이 나타남

- 작성된 3개의 파일을 동작시키기 위해 2번인 아이콘을 클릭하여, 다시 Wave를 선택(3번)하여 출력된 파형을 확인함(4번)

- 시뮬레이트 종료를 원한다면, 맨 상단 Simulate -> End Simulation 선택

감사합니다.

잘못된 정보나 오타 및 수정사항이 있을 경우 댓글로 달아주시면 감사하겠습니다.

'Embedded > FPGA' 카테고리의 다른 글

| [ModelSim/Verilog] 프로젝트 소스파일을 Edit 또는 더블클릭 시 메모장이 열리는 현상 문제해결 (5) | 2019.10.21 |

|---|---|

| [ModelSim/Verilog] ModelSim PE Student Edition 10.4a 개발도구 설치 (0) | 2019.09.23 |

| [Xilinx] ISE 14.7 Design Suite 개발도구 FPGA 업로드 방법 (5) | 2018.05.15 |

| [Xilinx] ISE 14.7 Design Suite 개발도구 호환성 문제 및 해결 (0) | 2018.05.15 |

| [Xilinx] ISE 14.7 Design Suite 개발도구 설치하기전 (0) | 2018.05.15 |